扫码添加微信,获取更多半导体相关资料

在氢氧化铵溶液中,使用各向异性硅蚀刻技术,在SOI晶片上制备了无连结fet(JL-FET)器件,以O2/N2电子回旋共振(ECR)等离子体作为栅极介质生长氮氧化硅,以反应性溅射作为栅极金属沉积硝化钛,利用扫描电镜成像和电学测量方法对其结构进行了表征,最终得到的硅通道厚度为65nm,器件的电性能与预期一致。

通常在几纳米内从1020个原子/cm3p型掺杂剂到1020个原子/cm3n型掺杂剂,相比之下,JLFET器件在整个器件中具有相同的掺杂浓度,从而降低了掺杂剂的扩散速率,除了使用标准的热退火和更少的离子注入步骤可以降低制造成本外,JL-FET也因其性能而脱颖而出,电流密度通过衬底[1]的厚度分布,参与电流的载流子为大多数类型,并且一些电荷散射现象可以通过极化栅在平带条件来减轻,这允许给定器件的更大电流。

在高频缓冲溶液中,使用湿式氧化和氧化硅蚀刻法将衬底变薄到约200nm,然后将晶片在50keV下离子注入磷,剂量为1013个原子/cm2,掺杂剂活化在1000°C的常规烤箱中惰性气体中进行30分钟,这一离子注入步骤的计划比通常剂量低,因为较低浓度的掺杂杂质会导致更宽的耗尽区域,通过牺牲一些电接触质量,在模拟步骤中只在25nm中观察到的晶体管行为,以及在更薄的器件中,即使在75nm厚的器件上也可以观察到,通过光刻技术确定了活性区域。

通过ECR等离子体培养氧化硅硬掩模,并在HF缓冲溶液中蚀刻,然后在氢氧化铵溶液中进行各向异性硅蚀刻,持续40秒,采用扫描电镜成像技术证实了湿式蚀刻过程,栅极氧化物是通过o2/n2ECR等离子体生长的氮氧化硅,栅金属由光刻和升降机定义,由溅射氮化钛制成,用光刻法和高频溶液蚀刻法对覆盖漏极和源区的氧化物进行蚀刻,用溅射法沉积金属垫片,最终退火分5分钟进行,在450°C的常规烘炉上形成气体(H2)。

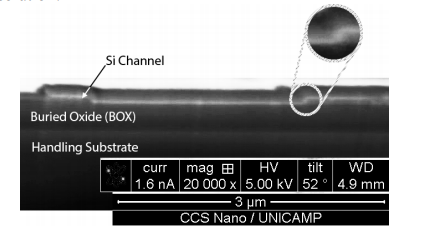

每个退火步骤后,在Keithley证明上测量装置I-V曲线,通过退火和电测量,使用Ga+聚焦离子束磨削和扫描电镜成像提取横截面图像,图1清楚地显示了预期的几何结构,使用图像编辑所进行的测量,软件结果表明,氢氧化铵溶液湿蚀刻后的通道厚度约为65nm,通道壁在(100)和(111)晶体平面之间的特征角约为57度,圆形边缘是在各向异性蚀刻过程中出现的元稳定(311)平面的结果,这些结果表明,在氢氧化铵溶液中使用硅湿蚀刻确实可以令人满意地减薄通道厚度。

图1

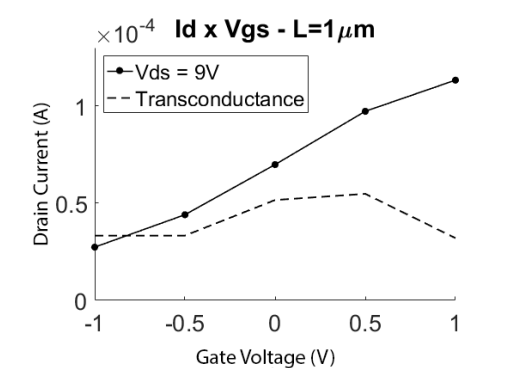

每个退火步骤后进行的电测量取得了不同程度的成功,显示最佳接触质量和晶体管行为的测量是退火20分钟后的测量,与预期的那样,大多数测量结果显示栅极电压对电流的影响减弱,如图所示2,这是因为在65nm通道厚度时,由栅极引起的耗尽区域不够宽,不足以耗尽每个载流子,器件的阈值电压变得非常负,并且器件在大多数VDS范围内作为门控电阻。在电触点质量较低,像肖特基二极管,扭曲了I-V测量,这是因为大约1017个原子/cm3的最终掺杂浓度在源和漏极区域不够高,无法保持欧姆接触。

图2

尽管由于其负阈值电压而不能作为开关,但IDxVDS结果表明发生了晶体管行为和低栅极漏电流,所制备的器件具有明确的三极管和饱和区域的晶体管行为,但不能实现截止。对氢氧化铵湿式蚀刻过程的进一步调整可能导致JL-FET设备的电气性能可与最先进的增强型MOSFET设备相媲美,因此,本研究证明了氢氧化铵溶液中的各向异性硅刻蚀是一种制薄硅基JL-FET器件通道衬底的可行技术。