扫码添加微信,获取更多半导体相关资料

硅片表面的金属污染物可能对其上制造的半导体器件造成不可逆的损伤,铜也不例外,它将减少少数载波寿命,减少DRAM的刷新时间,增加反向偏置结泄漏电流,这会导致栅氧化物漏电流增加,并降低栅氧化物的击穿电压,随着设备尺寸的缩小,这个阈值在未来可能会降低。

为了实现栅极氧化物完整性(GOI),通过斜坡电压试验确定缺陷密度,与时间相关的介电击穿是对设备保持运行时间长度的衡量标准,因此是可靠性的衡量标准,虽然使用了不同类型的晶圆,不同的引入铜污染的方法,以及不同的GOI指标,铜的植入、背面铜污染、化学浸渍污染和旋转污染都被用于在门氧化之前或之后引入已知数量的铜,有时氧化物缺陷密度(D),有时平均氧化物击穿场(Ebd)被报道为铜对GOI影响的测量方法,缺陷密度的含义在所有来源中并不一致,因为用于确定击穿的阈值在8MV/cm和12MV/cm之间变化,平均击穿场的含义在所有源中都不是均匀的,因为已经使用了不同的电容器区域来确定它们。

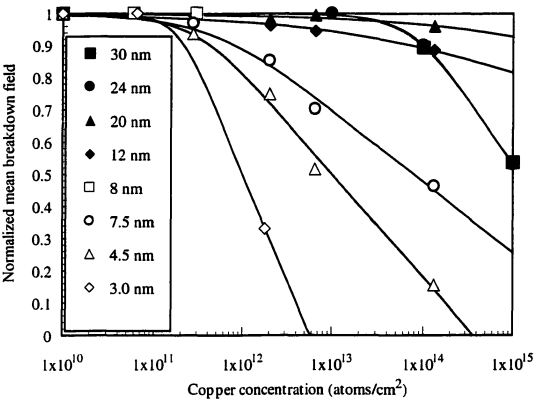

从图中可以看出,铜浓度有一个阈值,低于这个阈值,铜对平均击穿场没有可检测到的影响,如果铜浓度超过这个阈值,平均击穿场开始下降。一般来说,氧化物越薄,它下降得越快,这意味着保持加工条件尤其重要,以便在氧化物厚度较小时不超过允许的铜浓度,因为100种薄氧化物对产率的影响会更大,如果通过植入引入高剂量的铜,平均击穿场也会迅速降低,这可能是因为高剂量植入造成的损伤允许在(损伤的)表面附近有更多的铜沉淀。

利用透射电子显微镜(TEM),已经证明铜污染通过沉淀影响氧化物缺陷,在氧化温度上升时,铜可能很容易扩散到硅中,氧化前只有一小部分铜被并入氧化物中,铜很容易在硅中沉淀,因为它在硅中具有很高的扩散系数,并且其固体溶解度与温度密切依赖,为了发生沉淀,也必须存在成核位点,这些缺陷既可以是晶格缺陷,也可以是通过均匀成核而形成的缺陷。

由于高频溶液中的铜沉积与硅溶解同时发生,因此可能会发生硅粗糙化,这反过来又会影响生长在这个表面上的氧化物的可靠性,晶翅片(Cz型)在SPM和稀释的高频浴中清洗,然后将它们放在受铜污染的稀释高频浴中污染1分钟。染的APM溶液的铜污染达到一个稳定的浓度,可以用一个简单的吸附和蚀刻模型充分描述,如果在硅中存在足够多的量,铜可以在Si/SiOi界面上沉淀,导致巨大的产率损失,铜开始以这种方式影响产率时的阈值浓度取决于氧化物的厚度,对于薄于12纳米的氧化物,阈值浓度在2xlO“原子/cm”附近。

经过高温氧化的晶翅片对随后的铜污染不那么敏感,很可能是硅自身间隙的存在导致沉淀的核化和生长更加困难,或者它驱动铜进入取代位点。在栅氧化之前,硅表面的铜污染导致面积和场重叠成分的屈服损失,这是在野外重叠边缘的铜吸收和沉淀的结果。在介质电场中,可以看到一个大的与周边相关的栅极氧化物泄漏电流分量,这导致了现场重叠边缘的可靠性问题,这被Qbd测量证实,结漏电流还具有面积和周界分量,周长分量比预期的面积要大得多,因为铜的轮廓在表面附近达到峰值,由于当电路扩展到更小的尺寸时,器件的周长变得相对重要,周长产率和可靠性问题在高密度电路中占主导地位,因为铜被保留在场重叠边缘和表面附近,即使在低浓度下,它仍然是一个问题污染物。

研究发现,从受污染的HF溶液中沉积的非常低水平的铜会导致氧化物中高密度的凸起,研究表明,结果表明,这些凸起不是电短路,相反这些凸起的氧化物比周围的氧化物厚,SIANTRS投影的MOSFET栅极下凸点引起的电容变化将导致阈值电压偏移,这对于具有0.13微米特征尺寸且更小的设备技术来说是不可接受的。