扫码添加微信,获取更多半导体相关资料

晶体管的整体质量是金属氧化物半导体的主要问题之一,本文主要研究栅氧化层,在金属氧化物半导体晶体管中,包括对其质量的全面讨论,为了充分理解影响回顾了栅氧化层的晶体管结构,观察其性能的操作取决于其栅极氧化物的质量。

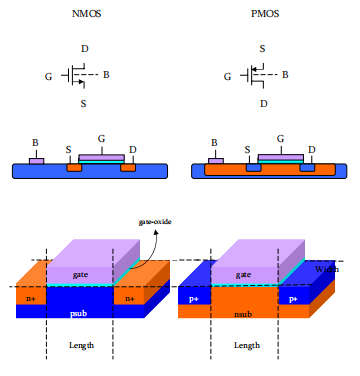

MOS晶体管是通过半导体分层过程产生的电压控制电流源。下面的图1显示了NMOS和PMOS设备的简化版本以及相应的电路表示,在结构上,晶体管由n型或p型(分别掺杂磷或硼)的大块硅衬底组成,连接方式为B,生长栅极氧化物绝缘层以将连接G的多晶硅栅极与基底材料隔离,最后将n或p型硅的两个植入区域分别创建源区和漏区,连接S和D。

图1

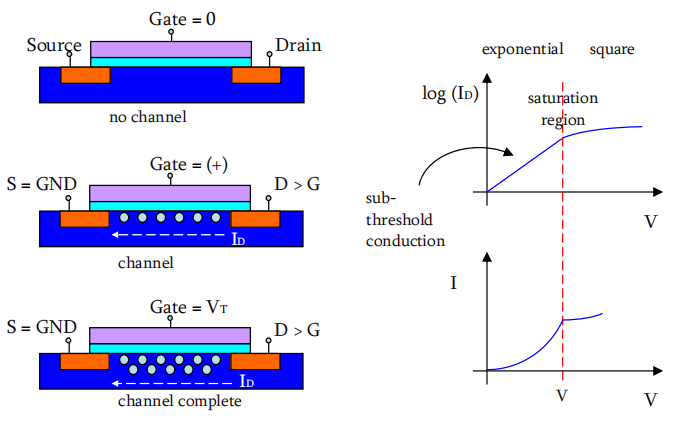

晶体管工作的基本原理非常简单,NMOS正电压应用到门,这开始画少数载体,即电子,门基板接口,施加到漏极的正电压(源极接地)将电子从源极扫描到漏极,产生电流,这是金属氧化物半导体工作中感兴趣的基本电流。下面的图2说明了这一点。

图2

图2是处于饱和状态下的MOS(典型的使用区域),在这种情况下,漏极电位总是高于或等于栅极电位,从图中我们可以看到,ID首先呈指数增长,然后是平方增长,正是在这个过渡点上,晶体管被认为是“开”的。此时的栅极电压被认为是阈值电压VT,可以清楚地看到栅极氧化物绝缘性质的重要性。理论上,通过氧化物的电位从基板中吸引载流子,在源极和漏极之间创建一个传导路径,而没有电流流入栅极,然而,在现实中,如果氧化物中存在缺陷,电流会开始迅速增长,需要有一套标准来确定栅极氧化物的质量及其成为完美绝缘体的潜力。

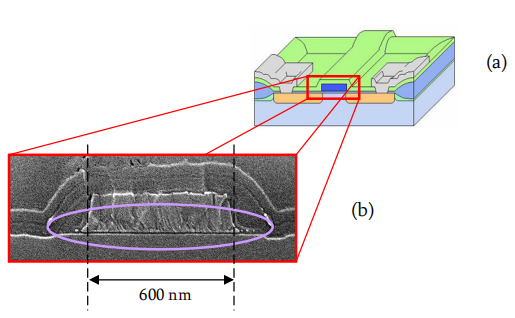

图3

下面的图3(a)显示了一个更详细的晶体管的三维图像,使用一个实际的扫描电子显微镜,SEM(b),更仔细地观察栅极区域,栅氧化物是用紫色圈出的非常细的黑线,栅极聚硅是在这条黑线上方形成的较浅的矩形,可以看到有效通道长度600纳米和栅极厚度12.2纳米之间的巨大尺度差异。

从上面可以看到,巨大的物理长度电流必须在晶体管中流动,而极薄的氧化层试图包含电流单独流向基板,而不是进入栅极,如此薄层材料中的任何小缺陷都可能对晶体管的质量造成灾难性的影响,应该包括对氧化物的电荷到击穿的完整表征。

如上所述,最终没有产生任何显著差异,大大提高了氧化物击穿值,并已作为永久标准工艺实施,在试验材料上的新汞冷启动工艺优于标准氧化物击穿,但在生产材料上的结果不同。因此,PRE-GATE步骤将没有任何永久的修复,虽然长期的表征和耗时的测试显示了对测试波动的改进,但本文表明,所获得的结果不一定能很好地转移到大规模生产车间,也不能反映在第二次测试的部分结果中

利用多种形式的应力测试,对一种12.2纳米的门氧化物进行了讨论和完整的表征,讨论了一种具有12.2纳米门氧化物的多点测试载体,并进行了完整的表征,此外在两个独立的清洗机器中分析了预栅极氧化物沉积硅的清洗步骤,并对几种新工艺进行了初步的评估和表征。不幸的是,最终的分裂没有显示出生产材料的分解性能改善,然而,这项工作将作为任何想要改进或描述晶体管栅氧化物的工程师来说,作为一个极好的起点,因为它提供了比生产测试更详细的测试结果。