扫码添加微信,获取更多半导体相关资料

为了研究通过无缺口硅蚀刻和湿法清洗最后一种工艺形成的小通硅孔(TSVs)的有效性,我们制造了一个具有阵列的薄芯片,引入静电卡盘级磁头,抑制薄芯片的扭曲,通过采用软材料凹凸,在低温和低压压载下堆积芯片,对薄芯片的TSVs和Si区域进行堆叠,对堆叠的芯片进行了4端和菊花链的测量,我们的实验证实,多层布线+TSV+凹凸连接表现出低电阻,菊花链完美连接多达38000个TSV。

作为一种实现小型,高速,高功能,低功耗电子系统的技术,该技术的应用领域有很多,其中之一是表面传感型三维结构高性能传感器系统,表面感测型传感器芯片和信号处理电路芯片分别制造,并通过使用TSV和凸块进行层压连接,具有以下优点:(1)容易采用与传感器匹配的工艺/材料,并且容易提高传感器的灵敏度;以及(2)由于布置的自由度增加,因此可以增加传感器面积比;另一方面,为了实现这一点,需要以低成本和高产率形成许多精细TSV,并在纵向方向上连接它们。

为了实现这一系统,我们专注于通孔最后的TSV工艺,该工艺的数量很少,并且易于降低成本,到目前为止,在晶片水平上,已经确认该工艺可以以高产率(约83%)形成直径约6微米的精细TSV,为了进一步确认这种精细TSV的有效性,我们报告了以高密度阵列排列精细TSV的薄芯片的形成和实际层压安装的结果。

首先,对8英寸的Si晶片进行边缘修整,通过3M晶片支撑系统,通过UV固化液体粘合剂将晶片安装在支撑玻璃上,然后使用研磨抛光机DGP8761HC,通过Si研磨和CMP将具有三层铝铜布线的晶片减薄至约26微米,然后使用FRA-5500iZa进行TSV形成光刻,此后,使用高速Si深蚀刻装置RIE-800iPB,通过博世工艺蚀刻Si,然后优化蚀刻时间以抑制凹槽的产生,然后使用反应离子蚀刻装置RIE-10NR进行二氧化硅蚀刻,使用的气体是氟甲烷和氧气的混合气体,在通过灰化去除抗蚀剂之后,使用低温CVD装置PD―200STP形成TSV的侧壁氧化膜,使用的气体为TEOS+O2,成膜温度为150℃,此后再次使用反应离子蚀刻装置RIE-10NR进行回蚀,以去除TSV底部的氧化膜,通过使用特殊的碱性清洁液对暴露的第一金属层进行湿法清洁,以清洁第一金属层(铝铜)的表面。该清洁液主要具有去除铝的氟化合物的效果,并且具有几乎不蚀刻第一金属层(铝铜)的表面本身的特征,在通过使用电离溅射装置进行Ar离子清洁之后,在相同的真空中进行钛铜的连续膜沉积,最后通过铜电解电镀填充铜之后,进行铜和钛的CMP,在各芯片上形成直径6μm的TSV阵列,通过电解电镀方法在TSV上形成相对软的铜-镍-焊料凸块,最后形成的铜-镍-焊料凸块的直径为8微米,高度为6微米。

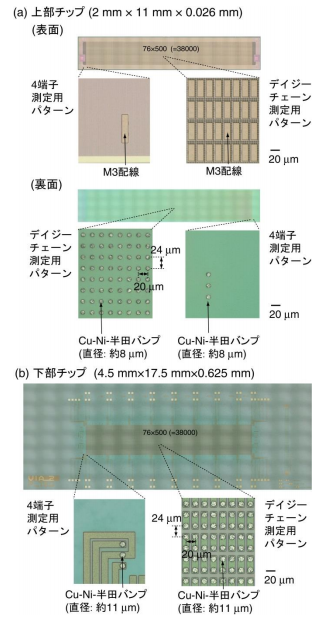

图3显示的是上部芯片和下部芯片的光学显微镜照片,上尖端为2 毫米×11毫米×0.026 毫米,下尖端为4.5 毫米×17.5 毫米×0.625毫米,通过层压这两个芯片,构成4端子测量图案和具有76×500(38,000)个TSV阵列的菊花链图案,并且可以测量多层布线+TSV+凸块连接部分的电阻和菊花链的电阻。

图3

在该测量中,由于测量的布线是上芯片中的第三层布线和下芯片中的第一层布线,因此获得的值是铜-镍-焊料凸块连接部分、TSV和多层布线的组合电阻,在薄芯片的四个位置进行测量的结果是102至112 MΩ,大致接近理论值。

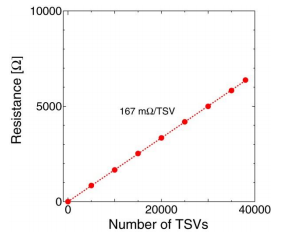

图6

图6显示的是包含38000个TSV以及凸块连接部的菊花链的测量结果,结果显示,菊花链被分成多个部分(1-5000,5000-10000,10000-15000,15000-20000,20000-25000,25000-30000,30000-35000,35000-38000),每个部分的电阻值被测量为TSV数(凸块连接数)和电阻的累积值,从图中可以看出,TSV数与电阻的累积值大致呈线性关系,因此薄芯片面内的电阻是均匀的。 此外,可以看出菊花链完全电连接到38,000个TSV。

为了证实通过vialast TSV工艺第一金属层的无切口硅蚀刻和湿法蚀刻形成的精细TSV的有效性,形成精细TSV以高密度阵列排列的薄芯片,随着相对较软的铜-镍-焊料凸块的引入、静电卡盘工作台头的引入以及低负载和低温安装的实施,薄芯片的翘曲得到了纠正,并且能够被均匀地层压并且没有损坏。此外,作为4端子测量和菊花链测量的结果,确认多层布线+ TSV +凸块连接部分的电阻值小,并且菊花链完全电连接(38000引脚)。这一结果有助于实现表面传感型三维传感器系统。