扫码添加微信,获取更多半导体相关资料

本研究表明了去离子(DI)漂洗和氧化物高频湿蚀刻过程对硅衬底的影响,利用硅片制备CMOS来研究硅坑的机理,分析了DI冲洗对摩擦电荷的影响。本实验的关键参数为每分钟转速(rpm)转速和时间,硅坑形成的孵育时间超过10秒,冲洗时间对硅坑的形成时间比rpm更有效,利用等离子体密度监测仪测量充电水平,研究了硅矿坑的形成机理和优化的冲洗工艺参数。

在制作CMOS器件的过程中,一般采用栅氧化层形成、PATON形成、去釉形成和双栅氧化层形成。此时,在通过在去釉和区域湿蚀刻抗蚀剂之前选择性地使用光掩模工艺来选择性地消除栅极氧化物的过程中,使用尺寸超过200纳米的HF、Si凹坑报告关岛的形成。据报道,这种Si坑将作为半导体器件的有源区,即晶体管的源区和漏区的缺陷,从而在半导体器件中造成严重的参数漂移和失效现象,因此迫切需要找出原因,找到最佳工艺条件。

本研究阐明了氧化硅界面带电现象引起硅坑的机理,指出了去离子清洗的核心参数,如时间和每分钟转数。通过缺陷检测装置观察刀槽花纹的出现程度。同时,利用等离子体密度监测器(PDM)装置阐明了电荷程度与Si坑出现程度的关系,从而揭示了氧化膜中的电荷现象可能是由摩擦电荷引起的,并进行了优化实验,验证了全清洗工艺。

采用KLA-腾科公司的KLA23XX模型作为检测硅坑缺陷的装置,获得硅坑出现程度的位置和晶圆图像图等信息。采用扫描电子显微镜(SEM)装置作为测定Si凹坑图像的装置,利用JEOL公司的倾斜SEM和日立公司的平面SEM进行分析。

为了找出硅坑产生的机理,在硅坑改进和优化实验中,测量了合格的去离子洗井转速和不同时间的电度。在测量的样品通过化学气相沉积在硅晶片上沉积氧化物1000之后,去离子洗脱条件由显影装置的显影单元在不注射显影剂的情况下实施几次。用PDM装置测量了制备样品的电荷分布程度和均匀性。在500和2000 rpm的条件下,时间为0至70秒,并且通过PDM观察晶片中的电压变化。

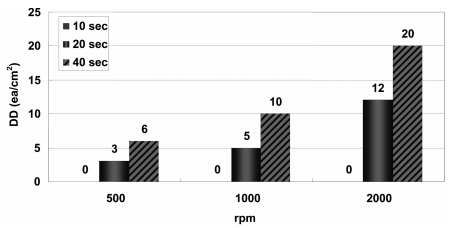

图2

判断Si坑的主要因素分别是500和1000。在2000 rpm下,9个样品进行去离子洗脱10、20和40秒。然后,通过去釉和缺陷检查观察是否形成硅坑,结果如图2所示。在DI清洗10秒的情况下,可以看出与rpm无关。完全没有Si坑,可以推断Si坑中DI水与晶圆碰撞产生的摩擦电荷较少,500 rpm条件下清洗时间为10。20.当缺陷密度增加到40秒时,它成比例地增加到6 ea/cm2,在1000 rpm时增加到5,10 ea/cm2,并且在2000 rpm时也呈现增加到0,12,20 ea/cm2的趋势,这进一步表明Si凹坑同时随着rpm的增加而增加,这表明,DI清洗时间是增加Si凹坑出现趋势的非常重要的因素,或者在10秒的情况下, Si坑不会在三rpm下出现,因此Si坑存在临界洗脱时间,洗脱时间与rpm一起对Si坑的形成起重要作用。

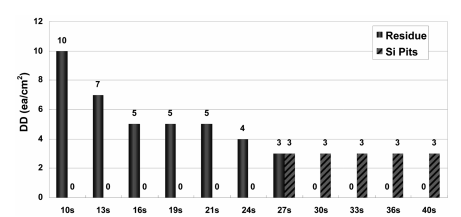

为了推导出DI清洗去除异物的最小时间,确定无Si坑的工艺时间,在500 rpm固定晶圆转数的条件下,清洗时间为10秒,条件为13、16、19、21、24、27、30、33、36、40秒,与之前的实验相同,后续的HVGX去釉工艺验证了去除氧化物后残留物和硅坑的产生程度,如图3所示,残留物的生成程度在10秒内达到10 ea/cm2,结果最大。

图3

此外,在反复氧化-HF刻蚀-碱性洗脱的过程中,Si衬底表面形成凹坑状缺陷,在Si膜上形成各种厚度的垫氧化物,用HF去除氧化物,然后用SC1重复进一步清洗。结果表明,坑的数量与重复工艺的数量成比例增加,这表明在用HF去除氧化物后,由于进一步的过蚀刻,硅表面缺陷中的硅被HF部分蚀刻,从而形成坑。

在半导体制造过程中,确定主要在使用等离子体的过程中研究的电荷转移对器件的影响也可以由不使用等离子体的光刻过程的因素产生。研究表明,在形成氧化物绝缘膜的情况下进行光工艺时,去离子清洗的影响是存在的,这与摩擦电荷现象引起的电荷现象密切相关。从这种研究中可以得出以下结论:1 .由于光刻工艺冲洗过程中DI洗脱的影响,在后续的高卷积去釉工艺中,可以确定HF处理的氧化膜在选择性消除过程中会产生Si坑;2.在成像过程中DI洗脱的因素中,确定洗脱时间和晶圆转数是与Si坑形成相关性较强的参数;3.利用PDM测量装置了解不同直喷洗井条件下的荷电程度,确定直喷洗井时间和转速可能产生摩擦荷电现象,这可能解释了在HF选择性去除氧化物的过程中,由此产生的氧化膜电荷转移可以促进缺陷中硅表面的局部刻蚀反应,并选择性地生成Sibits的机理。