扫码添加微信,获取更多半导体相关资料

本文章介绍了一种深垂直晶片孔和铜金属化射频硅集成的新方法,通过晶片孔通过深干蚀刻工艺实现,并使用铜电镀填充;提出了一种填充干蚀刻、高高宽比、紧密间隔间隙的新技术,并介绍了通晶片铜插头的制备工艺和电学表征,利用该技术,成功地实现了几种具有通晶片连接的新型射频结构。

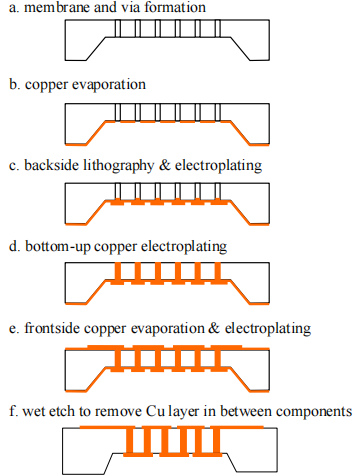

实现三维射频组件的工艺流程如图1所示,在这些实验中使用了标准的4英寸<100>硅片,采用各向异性湿蚀刻步骤,局部将晶片厚度降低至目标值(到晶片正面的期望距离地平面),在我们的实验中,使用了25-150µm厚的硅膜,通过膜的电感耦合等离子体蚀刻,实现了方形和圆形的高纵横比通孔,通过PECVD或LPCVD在孔的两侧或孔内沉积一个氧化物隔离层,在晶片的背面蒸发了20nm的Cr粘附层和300nm的Cu种子层,这种蒸发过程具有方便的特点,蒸发的金属不能深入内部。

图1

因此,铜岛在通道的底部附近形成,并迅速生长,这导致了通道底部的部分堵塞,这对于下一步的自下而上的电镀是非常理想的,采用光刻法确定这一侧的金属结构,并进行铜电镀,以增加这些结构的金属厚度,在这一步中,随着铜从内部的铜种子生长,通道的底部完全堵塞。

一旦达到晶片背面Cu结构的期望厚度,在这一侧施加光刻胶层,同时进行自底而上的铜电镀,直到孔完全填充,得到均匀的通晶片铜塞,然后在晶片的正面进行另一次铜蒸发,然后进行光刻和电镀,以实现这一侧的射频结构,然后去除树脂,并执行湿蚀刻步骤,将蒸发的铜剥离在射频结构之间,这样就实现了三维铜射频组件。

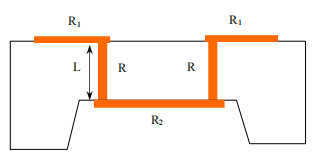

图5

为了评估杯塞的电性能,在设计和评估中包括了几种测试结构,一个电阻/阻抗测量结构的示意图如图5所示。该结构包括两个直径为40µm,长度为L(电阻=R),两个接触垫(R1)和底部电阻(R2),这种结构是在不同膜厚度(或不同L)的不同晶片上实现的。

利用电感耦合等离子体技术的透晶片蚀刻工艺已被用于通过膜的形成,不同形状和不同直径(5~50µm)的气孔已成功蚀刻,对于相同形状和尺寸的孔阵列,蚀刻参数在晶片上具有高度的各向异性分布和较大的均匀性,如果要一次蚀刻不同尺寸的气孔,则需要对工艺进行更多的调整。较大的蚀刻的更快,侧壁可能会变细。

对电阻结构进行了测量,并提取了电阻,孔内的平均铜电阻率为2.5x10-5Ωcm,与通常通过填充使用的掺杂多晶硅(大于10-2Ωcm)相比,这些铜填充孔的电阻率极低,这是非常有吸引力的,特别是需要非常高密度的应用,因此低电阻率是至关重要的。

综上所述,提出的一种新的透晶片铜电镀技术,这种铜插形成技术可以实现更高的集成密度和更好的射频器件,此外,后处理方法保持了与传统集成电路过程的兼容性,有利于在硅中进行无源组件和有源电路的集成,利用我们的技术实现了透晶片铜插头和新型的地下电感器、传输线、串扰隔离结构等射频结构,从而证明了该方法的潜力,通过电阻率得到的结果非常低,这使得该方法也非常适合于高密度的互连。