扫码添加微信,获取更多半导体相关资料

引言

在作为半导体光刻原版的光掩模中,近年来,与半导体晶圆一样,图案的微细化正在发展。 在半导体光刻中,通常使用1/4~1/5的缩小投影曝光,因此光掩模上的图案线宽是晶圆上线宽的4~5倍,虽然要求分辨率比半导体工艺宽松,但近年来,从边缘粗糙度、轮廓形状等角度来看,干蚀刻已成为主流。

半导体用光掩模是对在合成石英基板上成膜的铬、氧化铬、氮化铬等铬系薄膜进行图案化的掩模,特别是在尖端光刻用掩模中,现状是从硝酸铈系的湿蚀刻剂加工,基本完成了向氯、氧系混合气体的等离子蚀刻加工的转移。

实验

关于半导体光刻技术,在移位掩模技术中,多采用大小中最小间距的半数,在世代或技术节点上进行讨论。 到目前为止,为了实现更精细的技术节点,主要是通过光刻的短波长化来应对,但近年来,图案的精细化正在以超过短波长化的速度发展。

如表1所示,从180nm技术节点开始,晶圆上的解像线宽变得低于曝光波长,在今天的90nm技术节点中,变得不到一半有吗? 另外,关于预定于2007年开始量产的65nm技术节点,也在继续开发193nm波长下的曝光,现状是要求形成波长1/3的线宽。

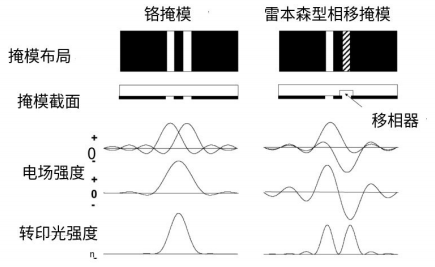

图2

图1、2简单表示各自的原理。 其中,半色调型除了使曝光光透过4%~20%左右并反转相位的半色调移相器膜代替铬遮光膜外,其掩模图案的设计、掩模制造方法等都与铬掩模相近。 因此,从图案尺寸与曝光波长相等或开始变小的250―180nm技术节点开始实用化。

一般来说,对于曝光波长形成的线宽足够大,转印对比度充分的光刻,MEEF为1。 也就是说,掩模的尺寸误差只在缩小倍率部分小,反映在晶圆上的状态。 另一方面,当形成的线宽小于曝光波长时,MEEF变大,有时达到2-3以上。 也就是说,转印对比度变小,掩模的微小尺寸误差被放大,成为晶片尺寸的误差。 因此,尖端光刻对掩模尺寸精度的要求加速增加,成为使掩模制造变得困难、成本上升的一个主要原因。

图3显示的是,对于铬掩膜和半色调型·Levenson型的各PSM,对波长:193nm的65nm技术节点的MEEF进行模拟的结果。

为了避免这种侧壁效应,提出了各种各样的提案,图5显示了具有代表性的三种方法。 第一个方法是图5(a)所示的底切法,是使基板挖入的侧壁后退,使其位于遮光铬正下方的方法。 该结构的特征是铬呈屋檐状突出,成为问题的侧壁隐藏在铬遮光膜下,因此,挖入部分的曝光光不会降低,挖入部分和非挖入部分的透过光量也不会有差异。 一般来说,该结构的屋檐强度较弱,在面罩清洗工序等过程中,虽然存在因物理冲击导致屋檐折断的危险性,但如果能使侧壁充分后退,在原理上是最有效的方法。

第二种方法如图5(b)所示,是通过抵消挖入部分和非挖入部分的透过率差,对掩模数据的开口部分尺寸进行偏置的方法。 该方法需要返回到掩码数据制作阶段的对应,有时需要复杂的数据处理。 因此,仅在面罩制造水平上的对应是困难的,设计者·面罩订购者的协助是不可缺少的。

第三种方法是图5(c)所示的双沟槽法。 这是以减少非挖入部分的透过光量为目的,在将非挖入部分·挖入部分的透过光间的相位差维持在180度的情况下,将两部分追加挖掘特定深度的方法。 但是,遗憾的是,已知该方法依赖于图案形状(节距·开口部尺寸等),需要调整挖入深度。 因此,有必要对每个设计的深度进行最优化,当各种设计混合在掩模上时,有时无法对所有的图案进行理想的解像。 因此,双沟槽目前只停留在特定的器件上。

在不加入底切的状态下,预计约28nm的尺寸差通过加入底切而变小,在140nm左右的底切中,转录尺寸差消失。 该底切的宽度根据光刻的条件和图案布局而变化,大约在100nm到150nm左右。 但是,对于65nm技术节点,可以设想掩模上的最小铬线宽为200―260nm左右。 在这种情况下,由于屋檐的强度问题,可能会出现难以加入上述100―150nm的底切的情况。 现在,掩膜厂商和掩膜用户之间,为了减少底切量,开始研究在图案数据的间隔宽度上加入偏差。 这是从掩模制造的优越性出发,延长底切结构的寿命,通过底切结构(图5(a))和尺寸偏差(图5(b))的融合来应对的想法。 在下一章以后,将对底切结构在掩模制造观点上的优越性进行说明。

关于光掩模,由于其原版的性质,具有不允许转弯缺陷的特征。 当然,构建不发生缺陷的掩模制造工序是最重要的,但考虑到成本方面,特别是尖端的光掩模,在发生缺陷时,通过修正缺陷部分,实现了无缺陷化。但是,在光掩模中发生的图案缺陷大致可分为白色缺陷和黑色缺陷。 前者是本来应该有图案的地方的遮光膜欠缺时的缺陷,另外,后者是本来应该是透过部的地方残留遮光膜时的缺陷。

各向同性蚀刻的湿法蚀刻产生缺陷的概率降低。 即使被加工表面被微小的剩余异物覆盖,蚀刻剂也会绕到,导致缺陷。这是不可能的。 另外,在我们采用的干法蚀刻后进行湿法蚀刻的方法中,还具有使干法蚀刻形成的微小玻璃缺陷不受湿法蚀刻的影响的优点。 因此,很大程度上抑制了难以修正的缺陷的发生。对于挖入玻璃类型的Levenson型相移掩模,蚀刻没有终点是其最大的特征。

此外,目前,为了满足相位差规格,在Levenson型相移掩模的蚀刻方面,出现了不是一下子进行规定的蚀刻,而是中途从蚀刻装置中取出一次,测量当时的蚀刻深度后,以计算出的蚀刻速率进行追加蚀刻的情况。 另外,在180度前暂时停止蚀刻,一点一点地反复追加,达到所希望的深度采取这样的方法。 在这种情况下,从追加蚀刻的稳定性等方面来看,湿法蚀刻是有利的,能够实现更高精度的相位差控制(中心值控制)。

结果和讨论

总结本文介绍了半导体光掩模中,湿蚀刻技术不可或缺的Levenson型相移掩模的现状。 结合湿法蚀刻的各向同性和干法蚀刻的各向异性,对于此前在平面上发挥功能的光掩模,导入立体结构,实现了能够延长光刻寿命的掩模。 目前,这种结构的Levenson型相移掩模已经在量产水平上用于部分用户的特定器件,对于65nm技术节点,其适用范围将会扩大。