扫码添加微信,获取更多半导体相关资料

引言

清洁是半导体集成电路生产过程中经常反复出现的一个过程步骤。它既可以从前一个过程中去除残留物,也可以为下一个过程准备表面。清洁和薄膜沉积过程的集成是至关重要的。氢氟酸最后一次清洗过程后的沉积延迟会导致环境暴露下裸硅表面的氧化物再生,或仅仅是表面的再污染。这将导致生长模式的改变或薄膜质量的恶化,并最终导致设备性能或生产的下降。

实验

这项研究使用了导体蚀刻室、电介质蚀刻室、微波剥离室和湿式清洁室的集群工具。清洁室基于Lam的受限化学清洁技术,使用清洁头以高流量流体流扫描晶圆表面,确保持续的化学物质补充和快速的副产品去除。清洁过程的暴露时间约为1秒。

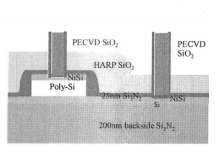

对于接触应用,图1使用了65纳米节点兼容的短回路流程,该流程由用于栅极叠层、隔离物和NiSi的标准工艺模块组成。最小尺寸为90纳米的接触孔在25纳米PECVD氮化物/90纳米高纵横比工艺HARP氧化物/200纳米PECVD氧化物的叠层上用“193纳米浸没光致抗蚀剂”构图。使用CO/O2/C4F6/CH2F2氧化物蚀刻和N2/CHF3 Si3N2开口的等离子体工艺顺序蚀刻晶片,随后是CF4/O2/N2微波带。随后,用不同的化学溶液清洗晶片,并研究干蚀刻/剥离和湿清洗之间的延迟时间对清洗效率的影响。用于清洁的化学溶液是去离子水DIW、稀释的氢氟酸HF,在DIW通常为1重量%,或氢氧化铵NH4OH-过氧化氢H2O2混合物APM,通常比例为1份29重量% NH4OH对5份30重量% H2O2对18份DIW 1:5:18.工艺流程为完成接触金属化物理气相沉积TaN/Ta阻挡层和电化学沉积铜以及基于铜/Aurora LK的单镶嵌模块。

图1 用于接触应用的叠层结构

扫描电子显微镜扫描电子显微镜照片是以自上而下的方向拍摄的。该工具配备了柱后Gatan成像过滤器tridiem-GIF,带有能量色散x射线分光镜EDAX和STEM装置。透射电镜样品取向为硅衬底的110°晶向平行于电子束。热解吸质谱在快速热处理器-大气压电离质谱仪室中进行,并结合VG的微量分析。

结果和讨论

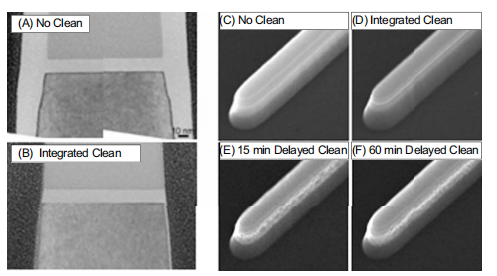

浅沟槽隔离刻蚀延迟效应的观察。在干法蚀刻和剥离浅沟槽隔离结构之后,不同厚度的残留物出现在沟槽侧壁上,如透射电镜和扫描电镜图所观察到的。图2A和2C,在含Cl2/O2的等离子体中产生的这些残留物是氯化氧化硅9,通常在蚀刻过程中用作侧壁钝化层,以获得所需的沟槽锥度。在68℃下,使用1%的氟化氢,曝光时间为2秒,蚀刻后残留物可立即清洗。图2B和2D,没有观察到垫氧化物的横向侵蚀。移除的能力使用相同清洁工艺的这些残留物随着蚀刻和清洁之间的延迟时间的增加而减少。1小时的延迟时间。与半导体制造中的正常排队时间相比,2F对清洁性能有很大影响,因此残留物没有完全去除。在短至15分钟的延迟时间内观察到这种效果。图2E椭偏光谱也应用于这些样品,并提供了侧壁残留物厚度的半定量分析。未示出的结果证实了扫描电镜的观察结果:用15分钟的延迟时间清洗的结构产生的清洁度水平介于原始“非清洁”结构和蚀刻延迟时间后立即清洗的“集成清洁”结构之间,大约为1分钟。

图2 利用TEMA和B、SEMC和F1%HF评估STI结构腐蚀后残留物去除和底物损失的腐蚀清洁延迟时间,2s暴露时间

多晶硅栅刻蚀延迟效应的观察。通过将基于TEOS硬掩膜的聚硅门蚀刻过程从硬掩膜和聚硅蚀刻步骤之间的光刻胶带步骤移动到完整的蚀刻过程的结束,被有意失谐以产生可见的残基。这导致了光刻抗蚀剂侧壁上残基的堆积,在过程序列结束的步骤中坍塌在结构的顶部。蚀刻后残留物在使用1%的氟化氢在68℃下蚀刻后立即可清洗,清洗暴露时间为2秒,这导致0.6纳米的氧化物损失。相比之下,使用相同的清洗工艺去除这些残留物的能力随着蚀刻和湿法清洗步骤之间的延迟增加而降低。1小时的延迟时间,与典型的fab排队时间相当,显示出对残渣去除的容易性有显著影响。

浅沟槽隔离和多晶硅栅刻蚀的延迟效应机制。使用氯气/O2和氯气/HBr/O2等离子体蚀刻硅基底,如用于STI和聚硅门蚀刻应用,会在工艺室的侧壁和器件结构上产生类似sioxcly的残基。通常存在一个成分梯度:表面层更富Cl、H和br,而体积层被氧化得更多。残渣层可以通过随后暴露于含o2的等离子体而深度氧化,如本研究中使用的干条带被氧化,在氧化物残留物中只留下微量的卤素。这种组合物解释了为什么蚀刻后的残留物很容易通过干燥蚀刻条带过程之后的高频湿清洁步骤去除。

作为延迟接触后蚀刻清洁的结果,观察到的电性能和相关产量的损失是一个重要的发现。使用先进的物理表征方法TEM、EDAX和EELS进一步研究了这种延迟时间效应的起源。对于“不清洁”和“28小时延迟清洁”的样品,在金属屏障/NiSi界面处明显检测到氧气。相比之下,对于具有集成清洁的样品,没有发现含氧的界面层。应该注意的是,这些含氧残留物不能通过随后的阻挡层沉积工艺的氩溅射预清洗来去除。该氧化物层最有可能在干法蚀刻和干法剥离过程中形成,并且很容易在蚀刻或剥离过程之后立即通过湿法清洗去除。与前面讨论的二氧化硅蚀刻后残留物的机理类似,含氧化物残留物很可能在暴露于洁净室环境期间老化和强化,使得它们更难通过湿法清洗或溅射清洗工艺去除。

总结

我们已经观察到由于干法蚀刻和湿法清洁工艺步骤之间的延迟造成的负面影响。使用相同的湿法清洗工艺去除蚀刻后残留物的能力随着蚀刻和清洗之间延迟时间的增加而降低。对于STI应用,观察到导致清洁效率降低的最短蚀刻清洁延迟时间为15分钟。对于多晶硅栅极和接触应用,延迟1小时后清洗性能下降,与半导体制造中的典型排队时间相当。在接触层面,观察到对电性能的有害影响:干法蚀刻/剥离和湿法清洁之间的1小时延迟时间导致接触电阻增加高达30%,产量损失高达25%。

使用更强的清洗条件是去除残留的浅沟槽隔离和多晶硅栅极或恢复电性能接触的一种方法。对于STI和聚硅栅的应用,这是通过使用更高的高频浓度或更长的时间来评估的。结果发现,在相同的净清洁暴露浓度和时间下,更短的化学清洁优于更长的清洁与更稀的化学。对于接触应用,通过从apm-切换到基于hf的清洁化学,获得了更具侵略性的条件,这成功地克服了延迟时间效应。然而,对于所有的应用,使用更积极的残留物去除过程来避免延迟效应是以牺牲更高的基底损失为代价的,这通常是不可取的。

干法蚀刻和湿法清洗工艺的集成可以增加工艺余量:对于相同的清洗条件,集成的蚀刻清洗序列比干法蚀刻和湿法清洗之间具有延迟时间的序列更稳健。或者,集成的蚀刻-清洁顺序能够使用宽松的清洁条件,以低衬底损耗实现良好的残留物去除。