扫码添加微信,获取更多半导体相关资料

摘要

三维集成电路技术已经发展成为半导体行业的新兴技术。硅片减薄是三维集成电路和硅通孔形成的关键技术之一。本文报道了三维集成电路硅片湿法刻蚀减薄技术。

介绍

通过应用摩尔定律,半导体已经小型化。然而,小型化的发展仍然是复杂性急剧增加和设备成本巨大的问题。另一方面,除了用于小型化的技术之外的技术已经被应用到高性能半导体的开发中。开发高性能半导体最有前途的技术是使用硅片(或芯片)减薄和硅通孔(TSV)的三维集成电路。这项技术为高性能半导体提供了以下优势:增加特定物理卷的内存容量;和更快的传输速度和更低的功耗,这是由于变薄和TSV效应提高了逻辑和存储器之间的响应能力。

实验和讨论

图1显示了蚀刻速率验证实验的结果。

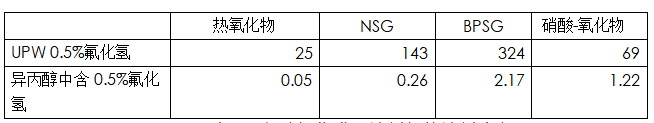

表3和表4显示了各种氧化膜的蚀刻速率以及根据蚀刻速率计算的它们对热氧化膜的选择性比率。与异丙醇溶液中的[1:24]相比,热氧化膜对水溶液中[1:3]的硝酸-氧化物的选择性表现出非常大的差异。这一结果表明热氧化膜不能被蚀刻,而存在可能蚀刻硝酸-氧化物的活性物质。用于本实验的异丙醇溶液中的氟化氢浓度明显小于水溶液中的浓度(1:0.03);然而,HF浓度实际上是相同的。这一结果表明,可能在异丙醇溶液中蚀刻硝酸-氧化物的反应物种被认为是中性的氟化氢。此外,硝酸-氧化物被认为不是完美的二氧化硅状态。

表3各种氧化膜对蚀刻剂的蚀刻速率

用旋转湿法刻蚀技术刻蚀硅片总蚀刻时间为1分钟,获得300 mm 10 mm的蚀刻量,总蚀刻时间为1.5分钟,获得450 mm 15 mm。这导致蚀刻量的均匀性为3%。此外,在晶片中心周围80毫米至100毫米的直径范围内,蚀刻量达到1%的均匀性。

总结

我们验证了通过使用全湿法蚀刻技术实现硅晶片的减薄而不会由于使用机械减薄技术(例如BG)而导致研磨损伤是可能的,并且展示了用于三维集成电路的高速率、精确硅晶片减薄蚀刻的潜力。结果,我们表明通过由HF和HNO3制备的混合酸化学溶液,在每片2分钟内减薄硅片是可能的。

文章全部详情,请加华林科纳V了解:壹叁叁伍捌零陆肆叁叁叁