扫码添加微信,获取更多半导体相关资料

摘要

描述了一种从硅和二氧化硅中去除氮化硅层的高选择性干法刻蚀工艺,并对其机理进行了研究。与传统的Si3N4去除工艺相比,这种新工艺采用远距离O2 /N2放电,CF4或NF3作为氟源的流量小得多。对于作为氟源的CF4,Si3N4的蚀刻速率达到超过30纳米/分钟,同时Si3N4与多晶硅的蚀刻速率比高达40,并且二氧化硅根本没有被蚀刻。对于作为氟源的NF3,实现了50纳米/分钟的Si3N4蚀刻速率,而对多晶硅和二氧化硅的蚀刻速率比分别约为100和70。原位椭偏法显示在多晶硅顶部形成约10纳米厚的反应层。该氧化的反应层抑制了反应性气相物质与硅的蚀刻反应。

介绍

硅局部氧化后氮化硅掩膜材料的剥离~LOCOS!是集成电路期间器件损坏的可能来源捏造。衬垫氧化物在过蚀刻过程中会退化。此外,蚀刻剂可以通过垫氧化物中的缺陷到达下面的硅衬底,并且以显著的速率蚀刻衬底。这种效应在基底上留下凹坑,称为“点蚀”。目前用于Si3N4剥离步骤的干法工艺有利于这种不希望的效果,因为它们蚀刻硅的速度通常比Si3N4快得多.因此,在二氧化硅和硅上选择性蚀刻Si3N4的工艺是理想的。

实验

实验用蓝宝石涂敷器在1000瓦的微波功率和600毫托的室压下进行。在大多数实验中,O2和N2的流量分别保持在800和110 sccm。这些参数被称为标准条件。

结果和讨论

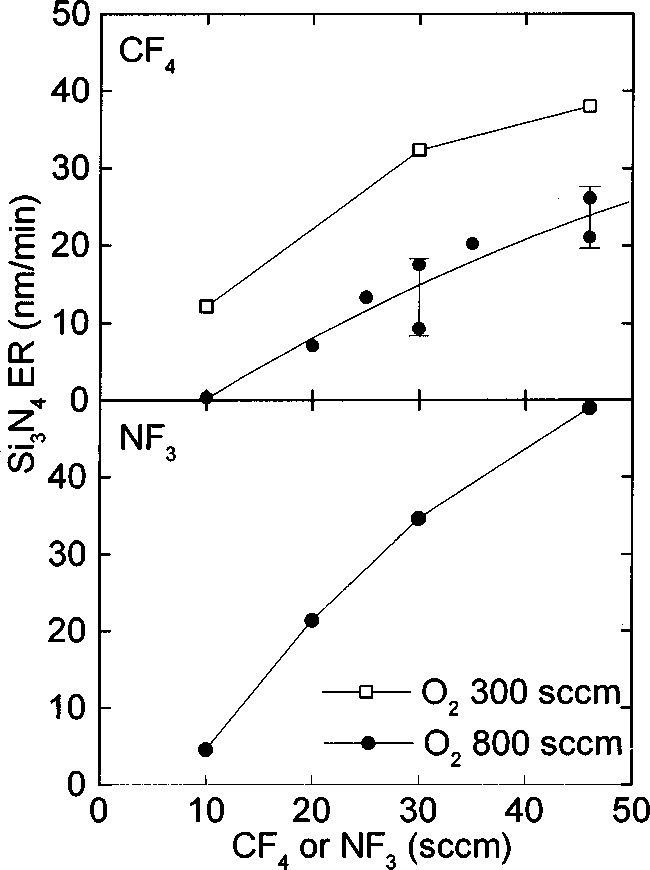

Si3N4蚀刻速率是作为添加到O2 /N2等离子体中的CF4的函数来测量的。三氟化氮被用作CF4的替代氟源。Si3N4的蚀刻速率测量在标准条件下进行,O2的流量保持恒定在800 sccm。Si3N4的蚀刻速率与NF3的流量成正比,如果使用NF3代替CF4,则蚀刻速率明显更高添加46 sccm的CF4。

图1 .Si3N4的蚀刻速率是CF4流量的函数

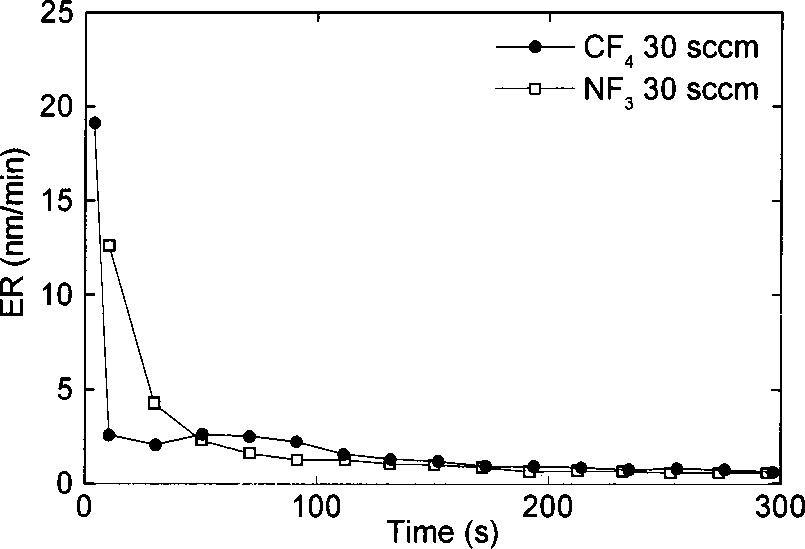

图2.标准条件下作为氟源的CF4和NF3的多晶硅蚀刻速率。在实验之前,样品被氢氟酸浸泡以去除自然氧化层。当在蚀刻过程中形成富氧反应层时,最初的高蚀刻速率被抑制

结论

一种新颖的远程等离子体化学干法刻蚀~CDE.已经证明了能够以大于30∶1的蚀刻速率比在硅和二氧化硅上选择性蚀刻Si3N4的工艺。它使用高流量的O2和N2,以及相对少量的CF4和NF3作为氟的来源。

对于这里报道的实验,氮化硅的蚀刻速率受到表面的氟原子流量的限制。一氧化氮含量丰富,不会影响Si3N4的蚀刻速率。这与向CF4或NF3放电中加入少量O2和/或N2的过程相反。

显著降低的氟原子密度,特别是对于CF4作为氟源的情况,不足以以比硅更高的选择性蚀刻Si3N4。此外,由室中的高一氧化氮密度提高的Si3N4蚀刻速率不足以获得高蚀刻速率比。从上面给出的数据可以得出结论,在硅的顶部形成蚀刻抑制反应层是实现高Si3N4蚀刻速率比的主要机制。原始硅表面的蚀刻以大约20纳米/分钟的速率进行。原位椭偏仪显示在蚀刻过程中,在几秒钟内,在多晶硅顶部形成反应层。反应层形成后,硅的蚀刻速率降低到与二氧化硅相当的水平。

最后,作者想建议,不完美的栅极氧化物可以通过这里研究的工艺来潜在地改善。蚀刻期间在硅顶部形成的反应层被高度氧化,含有一些氟,因此类似于栅极氧化物。在去除Si3N4之后的过蚀刻期间,栅极氧化物中空隙或缺陷下面的硅可能被氧化,因此改善了栅极的电性能。

文章全部详情,请加华林科纳V了解:壹叁叁伍捌零陆肆叁叁叁