扫码添加微信,获取更多半导体相关资料

摘要

在硅晶片上制造集成电路涉及数百个单独的工艺步骤。在处理的早期阶段,在将掺杂剂引入 Si 之前,通常很少担心 Si 从晶片表面通过氧化或蚀刻损失。与互补金属氧化物半导体器件的有源区的 <1 微米厚度相比,晶圆厚度通常 >600 微米,对于所有实际用途而言几乎是无限的。在利用轻掺杂外延层来提高器件性能的晶圆上,该层的典型厚度也相对较大,为 5-10 mm。通常,仔细控制各种清洁和氧化步骤对表面粗糙度的影响。通过化学清洗对硅去除的常规监测并未广泛进行。许多湿化学清洗方案用于制造,其中最流行的是由 Kern 在 1965.1,2 开发的 RCA 标准清洁 (SC1) 这种清洁的主要目的是去除晶片上的杂质,例如颗粒和金属表面。RCA clean 旨在通过两个步骤完成此操作。

实验条件和结果

通过晶片键合形成的市售 SOI 晶片用于这些实验。这些晶片是通过所谓的 SmartCut 工艺生产的,其中在键合前适当的氢注入有助于在氧化的 Si 衬底上形成薄 Si 膜。 5 起始晶片由 2000 Å 单晶 Si 膜组成由 4000 Å 的热 SiO2 与体硅衬底隔开。基板和薄膜在 (100) 平面上取向,名义上未掺杂,具有 14-22 W cm 的电阻率的轻度 p 型。SOI 薄膜在 1000°C 下通过几次牺牲干氧化变薄,从最初的 2000 Å 厚度降至约 120 Å。在每个氧化步骤之后,使用光谱反射法和/或单波长椭圆偏振法绘制生长氧化物和剩余 Si 的厚度。

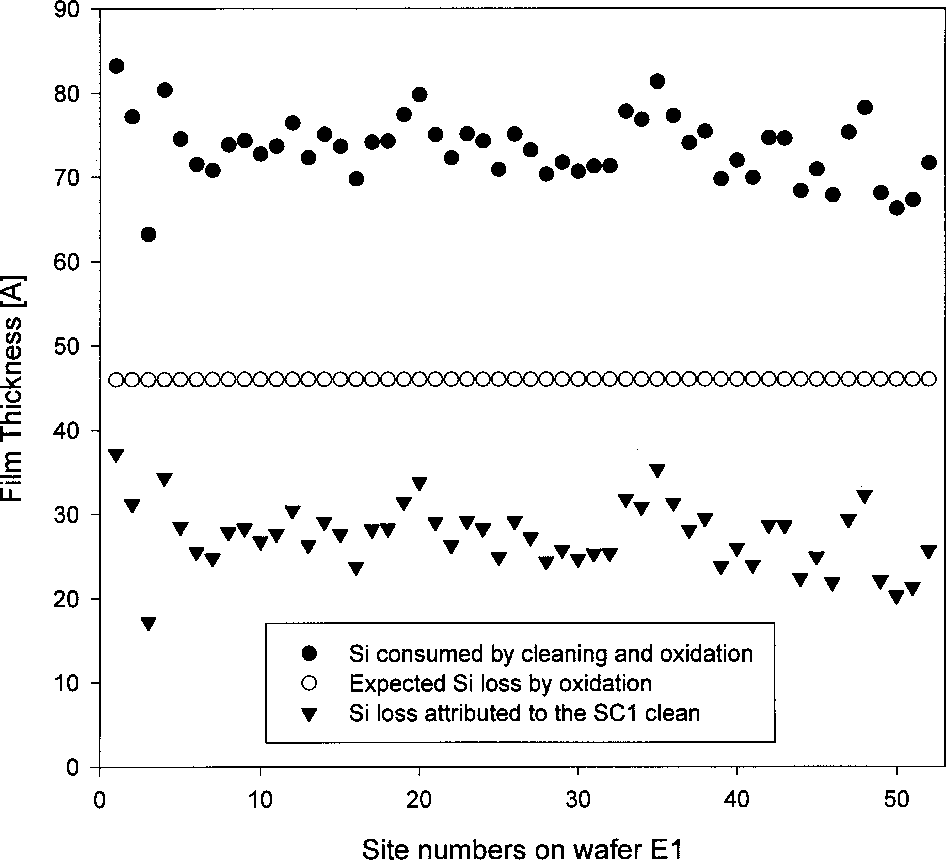

对于 Si 和氧化物厚度 >1000 Å,预测值和测量值之间的任何差异都在 2% 以下,在三层结构的实验精度范围内。(对于多层结构,实验不确定性大于单个薄膜。不仅所有薄膜的光学参数 n 和 k 需要众所周知,而且实验拟合假设完全突然和光滑的界面。)因此,对于较厚的薄膜,很难测量由蚀刻引起的 Si 厚度的小损失。当平均厚度为 120 埃的 Si 膜在 850°C 的干氧中进行清洁和氧化以获得 100 埃的衬垫氧化物时,很明显发生了严重的 Si 损失。

1. SOI 晶片的氧化率明显高于体硅,这是由于缺陷或由于薄 Si 膜中的应力;

2. SC1 清洁过程消耗了 25-30 Å 的硅。

由于在热氧化过程中 Si 填隙物被注入到 Si 中,我们一直在观察是否有任何迹象表明掩埋氧化物(它可以是填隙物的屏障或汇)通过其对填隙物浓度的影响来影响氧化速率。在一系列氧化过程中,SOI 晶片上生长了高达 3000 Å 的氧化物,体硅监控晶片和 SOI 晶片之间从来没有任何可测量的差异。在 100 Å 的 Si 上生长 100 Å 的 SiO2 也导致了正确的 SiO2 厚度,但 Si 短缺 25-30 Å。如果增强的氧化是造成 Si 损失的原因,我们将获得接近 160 Å 的 SiO2。

SC1溶液

由氢氧化铵 (NH4OH)、过氧化氢 (H2O2) 和水组成。H2O2 的主要目的是氧化硅,然后在 NH4OH 的帮助下溶解氧化物。将 Si 浸入 SC1 会导致不超过 6 Å 的化学氧化层生长,此时达到稳态条件,即 Si 的氧化速率和氧化物的溶解速率相等。 6,7 除非具体测量旨在检测硅消耗量,通常不会观察到硅的损失。有三种方法可以测量去除的 Si 量:

部分掩蔽表面的轮廓分析,4 (ii) 非常精确的晶圆称重,8 和 (iii) 相对于明确定义的深度标记的厚度测量。8 SOI 晶圆中的掩埋 Si/SiO2 界面提供了完美的标记. 一个原子锐利的界面可以放置在离表面足够近的位置,以便去除的厚度占总距离的很大一部分。

结论

SC1 清洁程序可去除有限量的硅。

文章全部详情,请加华林科纳V了解:壹叁叁伍捌零陆肆叁叁叁