扫码添加微信,获取更多半导体相关资料

还记得什么时候我们可以在星期天给手机充电,直到下周末才再考虑吗?曾经有一段时间,在购买手机时,电池寿命甚至不在前十名中。然而,如今,智能手机不断被用于计算、游戏、视频流和其他耗电的应用程序,因此电池寿命比以往任何时候都更加重要。

经典摩尔定律缩放曾经用于同时改进芯片“PPAC”——功率、性能和面积/成本——但由于 2D 缩放已经达到物理极限,情况不再如此。展望未来,PPAC 的改进将通过多种方法实现,包括缩小晶体管的新方法。简单地将晶体管做得更小已经不够了;我们还需要提高能效,以在小尺寸中提供最大性能。

延长移动设备电池寿命的一种方法是确保晶体管在应该关闭的时候真正关闭。理想情况下,当晶体管处于“关闭”状态时,不应有任何电流流过晶体管鳍通道和栅极。然而,在现实世界中,总会有少量电流通过沟道、结和栅极电介质泄漏(称为 I off)。因此,制造商不断努力将这些泄漏降至最低。

传统上,通过增加对门的控制来减少I off。FinFET 的创新就是一个很好的例子。在这个方案中,整个晶体管在垂直方向上被拉伸,使得沟道从衬底中凸起,栅极环绕鳍的三个侧面。在特定的 2D 封装中,栅极的较大接触面积可以更好地控制漏电流。

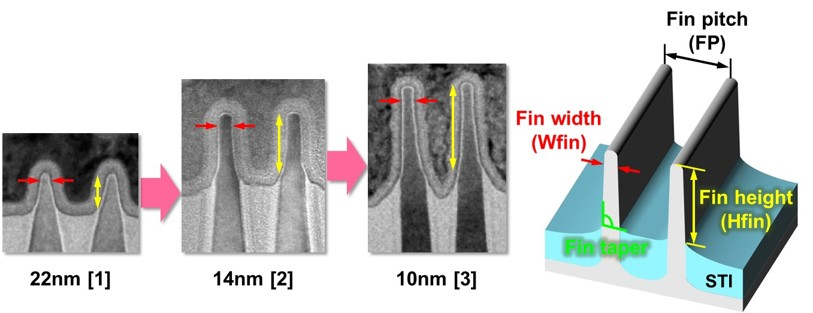

FinFET 的硅鳍片中的大部分驱动电流流向靠近材料表面而不是鳍片的中间,并且总电流几乎与鳍片周长(有效沟道宽度)成正比。这意味着当我们缩小鳍片和鳍片间距和/或减少每个晶体管的鳍片数量以在每个晶片上包含更多晶体管时,我们还需要使它们更高以进行补偿(图 1);然而,在减薄、成形和增加鳍片的高度方面存在重大的工程挑战。

图 1. 鳍片轮廓从 22 纳米到 10 纳米的演变表明更高和更窄的轮廓需要更高的驱动电流和更好的静电。示意图显示了翅片轮廓和关键物理参数。

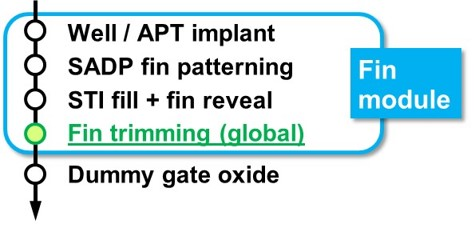

一个关键的缩放因素是缩小鳍片之间的空间或间距,以减少整体器件占用空间。以窄间距对窄鳍进行图案化非常具有挑战性,因此行业标准方法是将鳍图案化为可管理的宽度和间距,然后再对其进行修整。传统上,这是通过氧化鳍片顶部的几个纳米表面来实现的,然后使用湿化学在一个步骤中去除薄氧化层。这种“全局鳍片修整”方法以相同的速率蚀刻所有鳍片以获得最大的可控性,但也给先进设备带来了严峻的挑战。

图 2. 鳍片显示后全局鳍片修整的流程

整体翅片修整的第一个问题涉及修整后翅片的机械强度。在图 2 所示的流程中,翅片修整后有许多热过程,产生的应力对内翅片和外翅片产生不同的影响。这会导致鳍像孔雀羽毛一样散开,这种变形会导致鳍通道应力和通道流动性的差异。

第二个挑战是因为全局鳍片修整同时修整了沟道和源漏 (S/D) 区域。如果 S/D 变窄,访问阻力将上升并首先抵消鳍片修剪的任何好处。

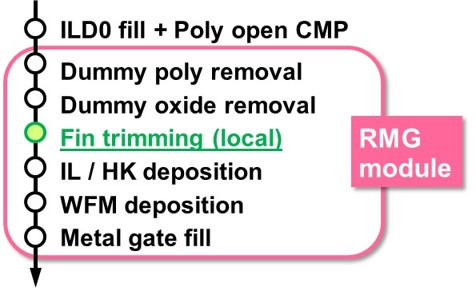

解决这些问题需要一种创新的方法来仅修剪通道区域,同时保持 S/D 区域不变。在这种“局部硅鳍片修整”方案中,如图 3 所示,未修整的鳍片在鳍片形成和金属栅极之间的步骤中保持最大的机械强度。因此,它们在后续步骤中不易变形。另一个好处这种新工艺的特点是 S/D 没有暴露,因此修整仅限于通道。这使我们能够创建我们需要的精确轮廓:窄通道、宽源极和漏极,翅片变形最小。

图 3. 去除伪栅极后局部鳍片修整的工艺流程为后续工艺步骤保留了鳍片的机械强度。

我们需要对氧化物和氮化物具有极高的选择性,以防止损坏隔离物或其他材料(低 k 膜)。在我们最近的论文中,我们通过精确的蚀刻控制和甚至改进的硅鳍线边缘粗糙度(LER 2.1nm 前,1.8nm 后)证明了该方案的可行性。

注意:此处包含的信息、建议和意见仅供参考,仅供您考虑,查询和验证,不以任何方式 保证任何材料在特定下的的适用性。华林科纳CSE对以任何形式、任何情况,任可应用、测试或交流使用提供的数据不承担任何法法律表任,此处包含的所有内容不得解释为在任何专利下运营或侵如任何专利的 许可或授权。