随着集成电路器件的纳米化、高密度化、高集成度及多层金属互连的进步,半导体技术节点越来越先进,对实际制造的多个关键环节也提出了更多新的要求。器件特征尺寸的不断缩小和三维器件结构的日益复杂性,使得半导体器件对颗粒污染、杂质浓度和数量越来越敏感。

据2019年1月28日报道,台积电南科14厂发生一起不合格原料污染事故,预估损失上万片晶圆,受到影响的主要是16/12nm工艺。NVIDIA的GPU芯片、海思、联发科的手机芯片以及一些ARM服务器处理器都使用了这一工艺,这也是台积电的主要营收来源之一。台积电发生的污染源已被确认,分别为前段刻蚀的铁离子污染和光刻胶原材料污染。前段晶体管受到污染可能会导致器件发生不正常的漏电,进而影响产品的良率、电学性能和可靠性。

2019年2月15日,台积电坦承,受到南科14厂污染事件影响,本季营收将减少约5.5亿美元。受到影响的客户包括辉达、联发科、海思和赛灵思等重量级客户,其中辉达的投片量超过上万片。考虑到此次事故涉及的是相对先进的16/12nm工艺,加上受到影响的股价大跌,台积电的实际损失有可能超过了40亿美元。如果再算上事故造成的停机以及产能和交付上的损失,则后果将更加惨重。

这一事件非常强烈地传递了这样一个信号,随着集成电路特征尺寸越来越小,半导体器件对生产工艺过程中的颗粒、有机残留物、杂质等污染物及湿法清洗的去除能力、缺陷控制、关键尺寸调控等的要求越来越高,同时对工艺化学品和金属离子等导致的污染越来越敏感,使得湿法工艺的关键性和重要性越发凸显。此外,芯片制造过程中的每个工艺步骤都有不同的控制和良率要求,特别是先进工艺要求制造过程中的颗粒尺寸越来越小,数量越来越少,缺陷密度也越来越低,这些都增加了工艺复杂性并带来越来越多的技术挑战。

技术节点演进带来的挑战

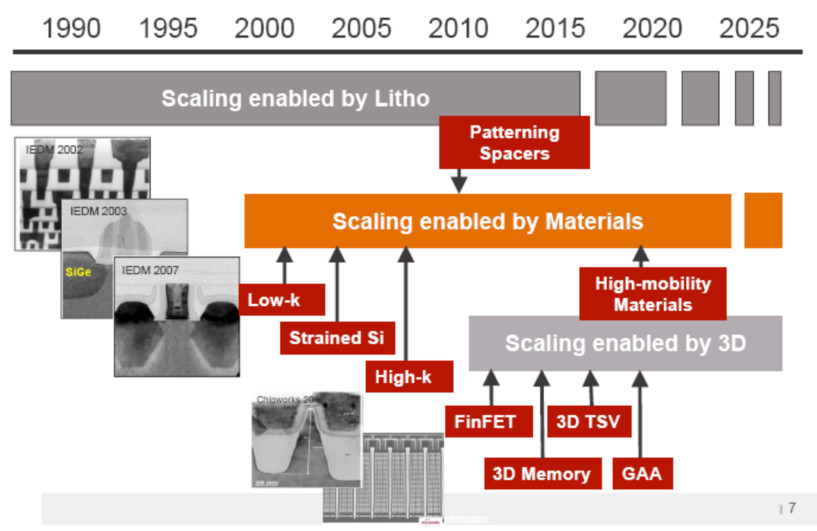

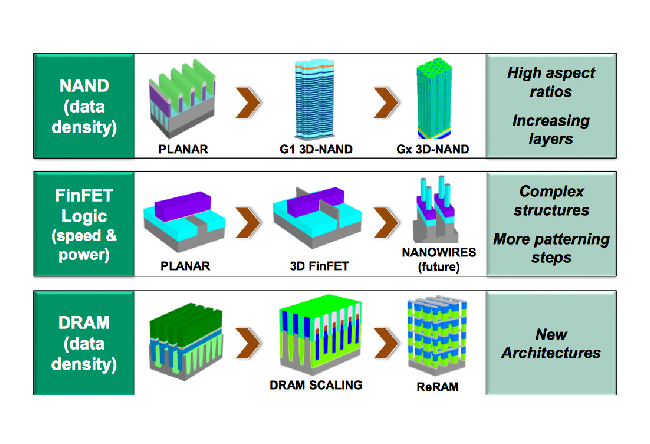

按照摩尔定律,集成电路器件特征尺寸每两年缩小0.7倍,尽管目前维持这一趋势所花费的时间越来越长。当前,随着半导体技术不断微缩,先进的集成电路器件已从平面向三维结构转变,集成电路制造工艺正变得越来越复杂,往往需要经过几百甚至上千道的工艺步骤。对于先进的半导体器件制造,每经过一道工艺,硅片表面都会或多或少地存在颗粒污染物、金属残留或有机物残留等,因此几乎所有工艺步骤都需要湿法处理。对于关键层来说尤其如此,往往需要经过多道清洗或湿法处理步骤。

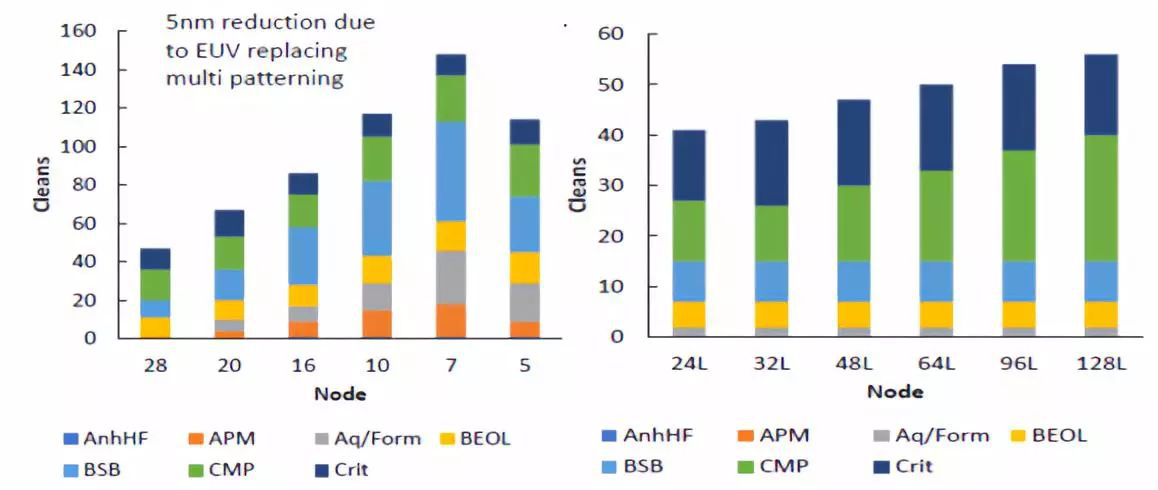

在20nm及以下技术节点,清洗步骤数量大约占所有工艺步骤数量的30%,而从16/14nm节点开始,更精细的三维器件结构、更复杂的前后端工艺集成、193nm浸入式光刻结合多重曝光技术及EUV光刻技术的引入等多种因素的推动,湿法工艺复杂性将进一步提升,湿法工艺的步骤也会根据特定产品的需求而有所增长。下图为IC Knowledge LLC 对逻辑器件和3D NAND器件的清洗步骤数量随工艺技术节点和闪存堆叠层数而做的调研数据,可以明显看到清洗步骤的变化趋势,显示出清洗在先进技术节点下的重要性和迫切性愈发增加。

对于先进技术节点,尤其是10nm、7nm甚至更小的器件。为了获得更高的器件可靠性及电学性能,湿法工艺不仅要能够从平坦的表面除去更小的随机缺陷、金属或有机离子沾污、特定材料和残留颗粒等,而且还要能够适应更复杂、更精细的三维器件结构带来的越来越多的要求,以免对器件造成不必要的损害或关键材料的损失,从而降低产量和良率。

表面损伤带来的挑战

半导体技术的不断演进,促进了更多新型材料在先进技术节点的应用,如高K栅介质、金属栅电极、新的硅化物、新型低k材料、新的互连金属钴等的引入,对湿法清洗选择比的要求越来越高,对前段和后段工艺都会带来新的挑战。如何调控和优化湿法处理工艺过程中不同材料间的选择比,是一道同时摆在湿法清洗技术和干法剥离(stripping)技术面前的难题。

对于先进技术节点下器件的清洗,一个非常明显的要求是在去除过程中要避免对图形造成额外的损伤。因此,当使用某一类清洗液进行处理时就必须了解器件结构上的薄膜材料和组分的构成及其比例关系。比如,在接触孔清洗中,为了得到良好的电学接触表现,需要去除接触孔底部的自然氧化层,但是如果接触孔氧化物薄膜的密度低于热生长氧化物,则会导致其刻蚀速率非常快,图形形貌及质量受到无法预料的影响,所以必须保证清洗工艺过程中的选择比。再如刻蚀栅电极之后的去胶工艺、离子注入后的去胶工艺都可能导致大量的硅衬底损失,尤其是当这个过程需要重复很多遍时,材料的损耗预计将更加明显,将对器件的电学性质造成显著的消极影响。

因此,在半导体前后段制造中,为了降低材料表面受到的损伤,对材料间的选择比要求越来越高,湿法清洗技术面临的挑战也日益突出。

高密度三维器件带来的挑战

对于平坦的表面来说,面临的困难主要集中在化学清洗方面;而对于三维结构来说,严密控制材料损失的清洗工艺对于FinFET、3D NAND和其他3D结构至关重要,因为不恰当的处理可能会导致图形损伤,特别是由于批处理晶圆的非均匀性,由此带来非常明显的器件电学性能恶化和可靠性问题。对于这些新型的器件,由于结构本身的复杂性,使得无损伤并能有效的去除表面颗粒变得非常困难。对于具有高纵横比结构的存储器件来说,残留物必须完全去除,并且不能对结构带来机械性损伤或过多的侧壁侵蚀。

三维结构的引入,多种不同种类的材料集成在同样的系统中,如何确保在去除颗粒的过程中,不损伤到器件结构本身,并保持合适的工艺窗口和工艺精度是摆在当前半导体集成电路制造过程中的重大难题。过去经常采用的兆频超声波搅动这样的常规物理清洗方法会对器件结构的损伤和图形坍塌等有潜在影响,需要根据具体的产品特点,优化、改进或采用更好的处理方式,以便在保持微粒去除工艺效率的同时不对图形完整性产生有害影响。

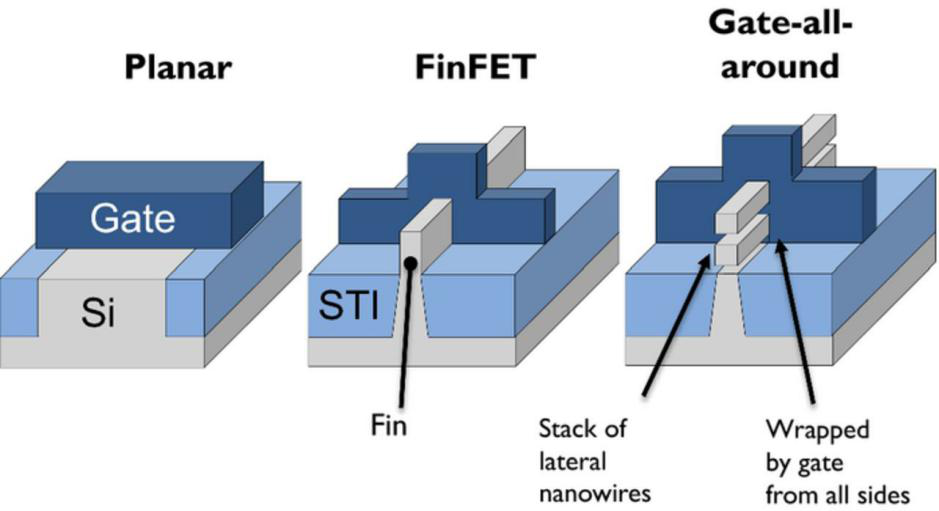

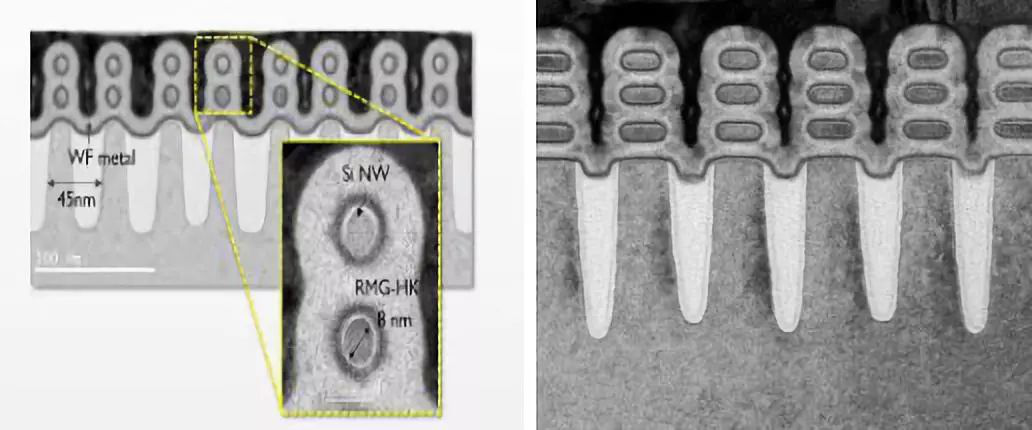

堆叠式围栅纳米线器件提出的挑战

当前,FinFET器件已经在22nm节点开始了应用,有望推进到5nm技术节点。继续向下发展,FinFET器件将遇到更多困难,而垂直堆叠式围栅纳米线器件由于对短沟道效应(SCE)和漏致势垒效应(DIBL)具有天生的免疫性,极好的静电控制能力,极高的电流开关比和缩小尺寸的能力, 已成为集成电路技术发展路线图5nm技术节点以下的有力竞争者。

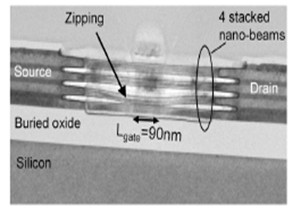

尽管这种器件具有许多突出的优点,可堆叠式围栅纳米线的制备技术则极具挑战。有报道显示,在纳米线制备过程中发现,四层结构容易在相邻纳米线间发生粘连而三层结构则无类似的现象。这可能是因为由于采用了SiGe外延工艺,为了避免超晶格中的应变弛豫,Si层间的SiGe的厚度必须被大幅度降低。在采用湿法工艺释放时,溶液中的表面张力很容易诱导相邻两层之前纳米线的相互粘连,导致纳米线无法正常释放。

为了半导体清洗技术能满足不断出现的新需求,必须根据产品或具体工艺的技术特点对现有制造工艺进行针对性的调整和修改。当前,堆叠围栅纳米线的制备主要采用后释放工艺以便与现有的FinFET器件制备技术有良好的兼容性,但难点在于如何在纳米尺度范围的栅极沟槽中去除SiGe牺牲层材料。

在这种情况下,干法清洗技术逐渐进入人们的视野,而采用HCl气体去除牺牲层释放纳米线的方法得到了广泛应用。与传统湿法清洗技术不同,这种技术需要采用新型的干法清洗设备。在SiGe牺牲层去除过程中,要避免对两侧SiGe层产生过多的横向腐蚀,从而影响后续的栅氧化层和高K金属栅材料的填充,这无疑增加了工艺复杂性和集成难度。

未来与展望

随着集成电路器件尺寸持续缩小,清洗工艺过程中的材料损失和表面粗糙度成为必须关注的领域,将微粒去除而又没有材料损失和图形损伤是最基本的要求,因此必须考虑周全并有所折衷。湿法清洗工艺的效果既取决于所采用的湿法工艺化学品,还与所采用的设备密切相关。为了推动湿法清洗技术的快速发展,需要化学品企业、设备生产商与芯片制造商紧密协同,在技术上不断创新,而合作开发定制化的化学品将是未来的重要趋势。

另外,未来干法清洗技术有望在先进器件上得到更广泛的应用,主要应用于对选择性要求非常高的表面清洗步骤上,这推动了各种更多创新技术的研发,例如超临界CO2(Super Critical CO2)清洗。

多年来得到广泛应用的各种商用清洗技术是解决当前所面临的一切挑战的基础,而各种新材料、新技术、器件和新结构等的大量出现必将推动半导体清洗技术的快速发展,并持续满足半导体集成电路制造提出的越来越严苛的技术需求。

免责声明:文章来源于网络,如有侵权请联系作者删除。