扫码添加微信,获取更多半导体相关资料

本文我们展示了一个使用纯湿法方法的清洁过程的性能,光刻胶和侧壁聚合物的去除是通过结合浸泡和使用环保化学方法的高压喷雾工艺来完成的,这减少了流程步骤的总数,从而降低了总体成本,先前的工作表明,物理分析,包括SEM、EDX和Auger,以及电气测试,都需要确定清洁度,本研究的重点是电气测试,以确定仅湿清洁的性能。

通过硅通(TSV)技术允许通过芯片垂直进行电气连接,当集成到设计中时,该技术可用于减少互连长度,减少软件包的大小,并增加芯片之间的带宽。在博世DRIE蚀刻过程中,这是通过交替进行的腐蚀性蚀刻步骤和含氟聚合物沉积来完成的,各种清洁的工艺被用来从TSV中去除这种聚合物材料,我们展示了一个使用独家湿式方法的新湿式清洁过程的性能,使用电气测试进行性能评估,并使用物理计量学进行验证。

每个晶片在精确控制的条件下浸泡在加热、循环、溶剂浸没浴中,测序基于下游工艺时间,确保芯片浸泡时间相同,通过适当的化学性质,浸泡时间允许光刻胶的溶解和去除侧壁聚合物涂层,浸泡后,溶剂湿晶片被运送到一个单晶片自旋工艺站,以完全去除残留的光刻胶和侧壁聚合物,高压化学风扇喷雾的使用增强了残差的去除。冲洗过程确保了晶片的完全清洁和无颗粒。

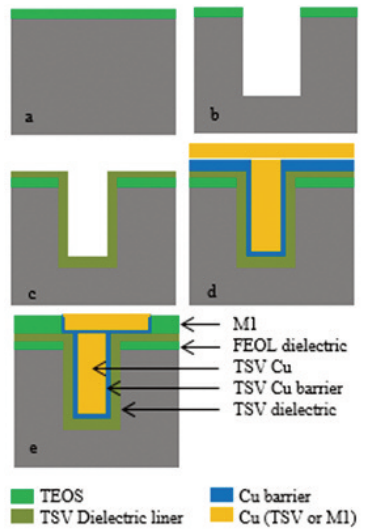

工艺流程如图2所示。正硅酸四乙酯(TEOS)薄膜首先沉积在(a),蚀刻TSV与由臭氧/TEOS热化学气相沉积过程(c),形成的氧化物排列铜屏障和种子膜被沉积,铜被电镀到TSV(d),中使用CMP去除TSV-Cu覆盖层,并在TSV(e)上方形成单一大马士革金属。

图2

实验设计采用新的Veeco湿清洁代替现有的dHF/nh4OH:h2o2湿清洁,并代替灰和现有的湿清洁,去除灰分步骤可将RIE处理时间减少33%。POR是有记录的过程。用电气测试来评价清洁过程的性能,显示了测试设置的示意图。我们测量低压下基底的泄漏电流,然后以阶梯式斜坡电压,以找到TSV介质断裂的电压,在我们的标准配置中,正电压施加于CuTSV,我们使用光学照明产生少数载流子,并增加一个延迟,允许tsv氧化物硅电容器为充电。

使用表中的配方表对5x50tev处理的步骤进行清洗。研究了三种不同的浸泡时间,每次进行两种冲洗过程,变化总共运行了三次,此外,使用我们的POR并行处理五片晶,在没有湿清洁的情况下处理两片,图2显示了在5v时从tsv到晶片背面的泄漏电流,每个分裂的细胞使用条形和胡须图显示,在每个晶圆上测量了32个直径,用于分裂细胞的所有晶圆都被结合在棒状体和晶须中。

没有湿清洗的分裂细胞与使用我们的标准SC1和高频清洗的晶片类似,这表明TSVis中的聚合物主要通过灰分过程去除,与标准工艺晶圆相比,在Veeco清洗过的晶圆均显示有泄漏电流的微小增加,浸泡时间和冲洗过程不影响可重复方式的泄漏电流测量。

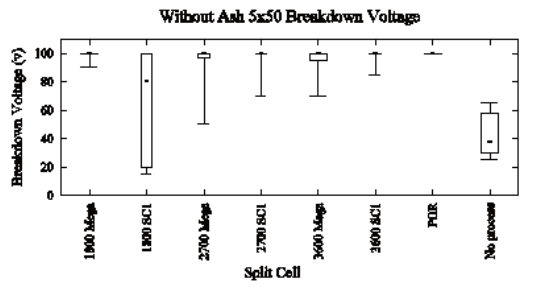

图5

击解波电压如图5所示,PORsplit电池中所有死亡设备的故障电压均大于100v,所有没有清洁工艺的模具都在60v前失败了,在Veeco清洗的薄片有一些模具在100v以下出现故障,随着清洁时间的增加,有更好的性能的趋势。在Veeco清洗过的晶圆的性能稍好,这表明有一些材料需要去除。在Veeco清洗的晶圆与POR晶圆有相似的泄漏,外围模具具有较低的测量电流,浸泡时间对泄漏电流的影响不大,无灰点2x40的故障电压,随着清洁时间的增加,外围模具显示出性能更好的趋势。

电气和物理分析表明,Veeco湿清洁可以从tsv中去除光刻胶和侧壁聚合物残留物。Veeco湿清洗过程已经证明了基于泄漏电流和介电击穿电压与POR相似的结果,同时消除了灰分,这是等离子体过程的重要组成部分。数据中的额外扩展代表了大晶圆间和晶圆内的变化,这可能是由于演示工具的手动特性以及从演示站点发运和返回晶圆所需的额外时间。总的来说,Veeco湿清洁工艺显示了等效电气结果,通过消除等离子体灰降低了成本。